when trying to trigger the artiq hardware with external envent, I encountered some strange problems: the "duration of gate_rising(duration)", and the number of "controlls in the with parallel block"(less than 8 controlls) will make the output signals incorrect.

I use the "gate_rising", "timestamp_mu()", and "at_mu()" functions. please see the example code below.

@kernel

def run(self):

self.core.reset()

self.ttl8.input()

self.ttl9.input()

self.test_trigger1.output()

self.test_trigger2.output()

self.AOM_rf_switch_TTL.output()

self.AOM_rf_choose_TTL.output()

self.PD_signal_sw.output()

self.AWG1_ch1_trigger.output()

self.AWG1_sw_TTL.output()

delay(10 * ms) # time for the artiq init.

pulsetubegate = self.ttl9.gate_rising(100 * ms) # waiting for external trigger

at_mu(self.ttl9.timestamp_mu(pulsetubegate))

delay(1*ms)

self.test_trigger1.on()

delay(10*us)

with parallel:

self.AOM_rf_choose_TTL.on()

self.AOM_rf_switch_TTL.on()

delay(5*ms)

with parallel:

self.AOM_rf_switch_TTL.off()

self.test_trigger1.off()

delay(10*ms)

with parallel:

# =======start of code block 1

self.AWG1_ch1_trigger.on()

self.AWG1_sw_TTL.on()

# ====end of code block 1

self.test_trigger1.off()

self.test_trigger2.on() # the 1st test_trigger2 on

delay(0.1*ms)

with parallel:

self.AWG1_sw_TTL.off()

self.test_trigger2.off() # test_trigger2 off

delay(10*ms)

# ====start of code block 2

with parallel:

self.AWG1_sw_TTL.on()

# delay(10 * us)

self.test_trigger2.on() # the 2nd test_trigger2 on

# ==== end of code block 2

delay(0.2*ms)

self.AWG1_sw_TTL.off()

delay(10 * us)

self.test_trigger2.off() # test_trigger2 off

delay(10*ms)

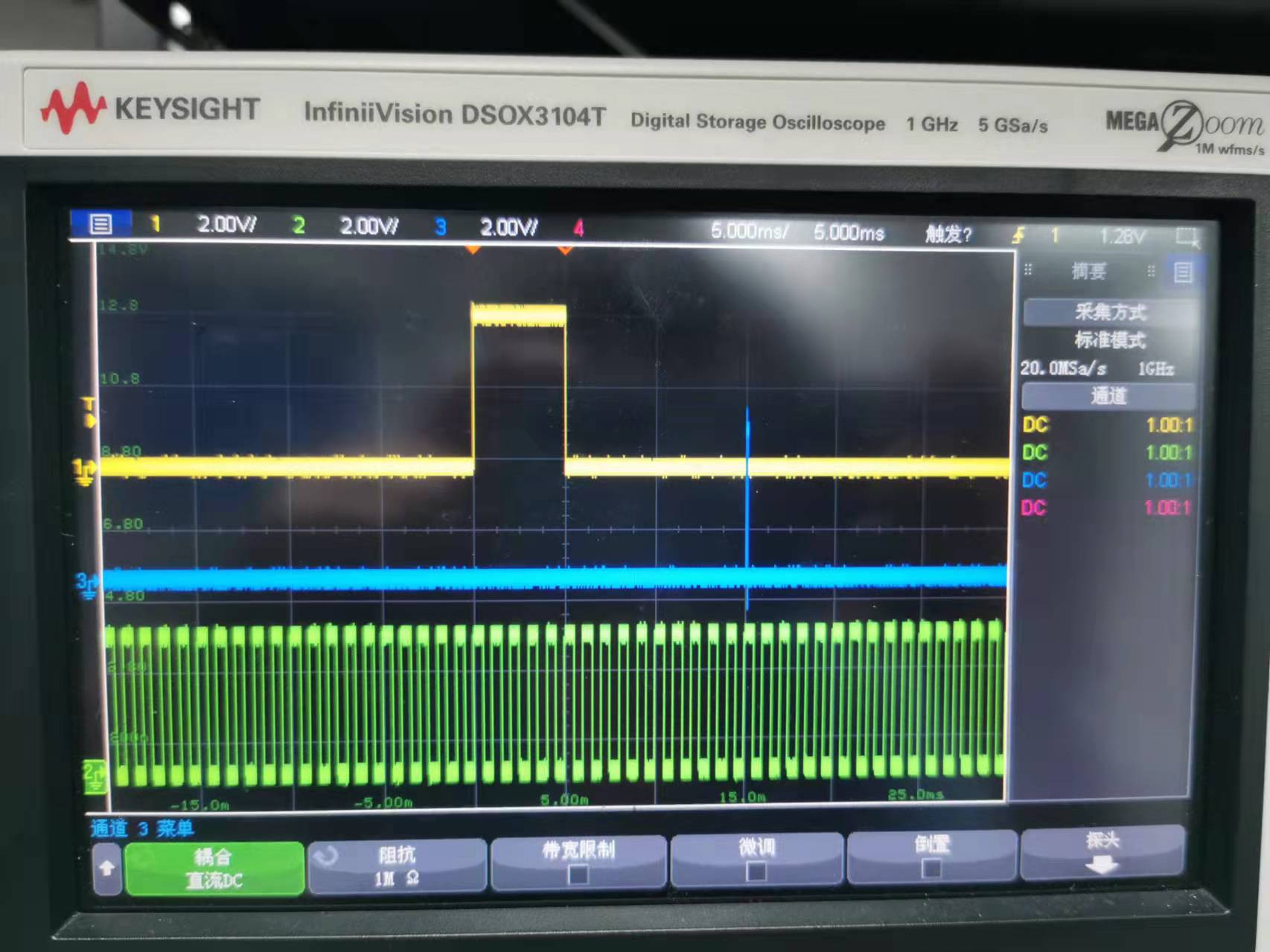

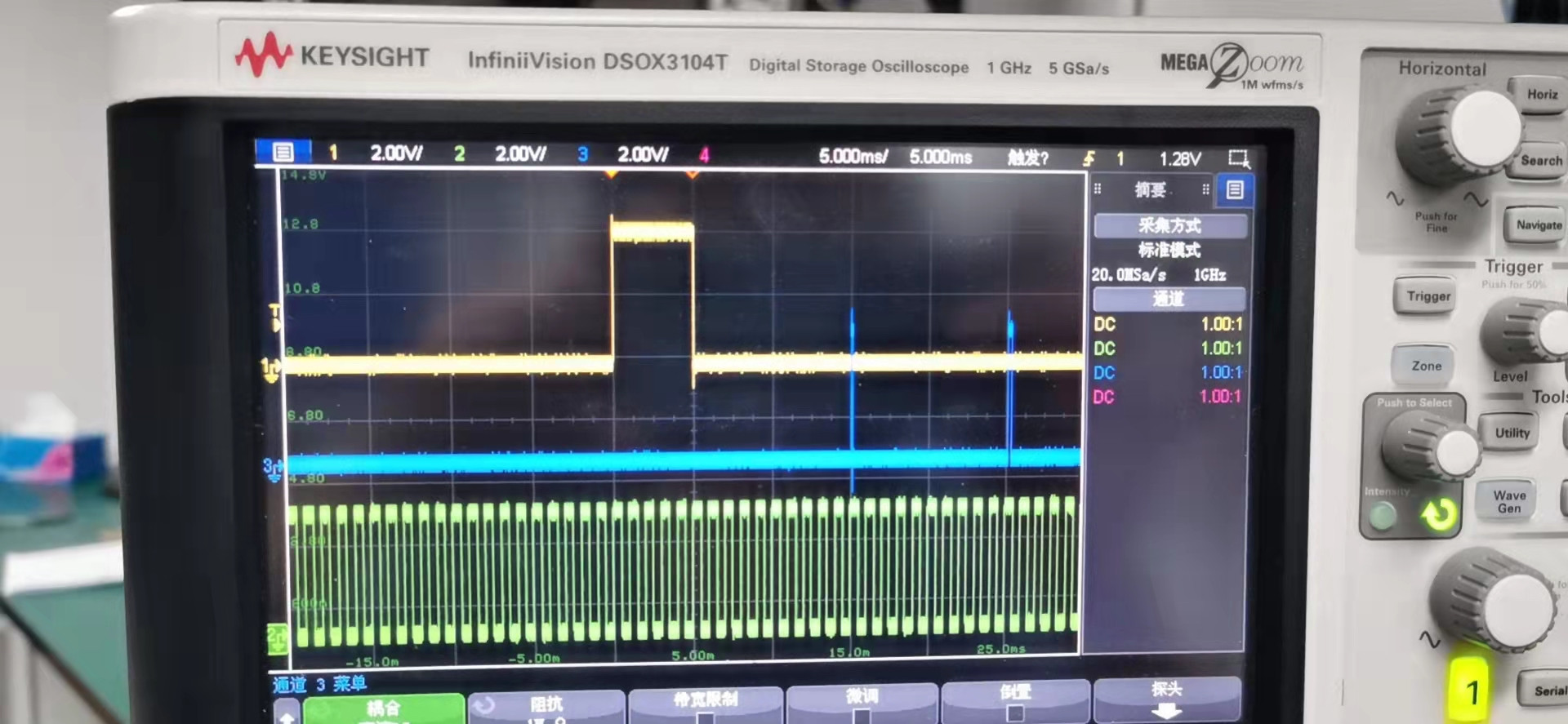

for this code, the output is incorrect ,see below: (yellow:chn1, test_trigger1; green: chn2, external trigger, conected to ttl9; blue: chn3, test_trigger2)

if i comment the code block 1, as follows:

...

with parallel:

# =======start of code block 1

# self.AWG1_ch1_trigger.on()

# self.AWG1_sw_TTL.on()

# ====end of code block 1

self.test_trigger1.off()

self.test_trigger2.on() # the 1st test_trigger2 on

...

the output is correct (the chn3 has 2 pulses )

if the gate_rising(duration) is 10 ms, and the code block 1 is un-commented, the output is corrent (chn3 has two pulses)

if the gate_rising(100*ms), the code block is un-commented, but the code block 2 is modified as

# ====start of code block 2

# with parallel:

self.AWG1_sw_TTL.on()

delay(10 * us)

self.test_trigger2.on() # the 2nd test_trigger2 on

# ==== end of code block 2

the output is correct.

I donot reflash the gateware to the newest version. the artiq gateware is 6.7621.d9b01ed8; the software is 6.7654.56b8c3c0.