Hi @chaiyu02! I'm helping look into this case. I've also been able to reproduce the rising time phenomenon with my oscilloscope.

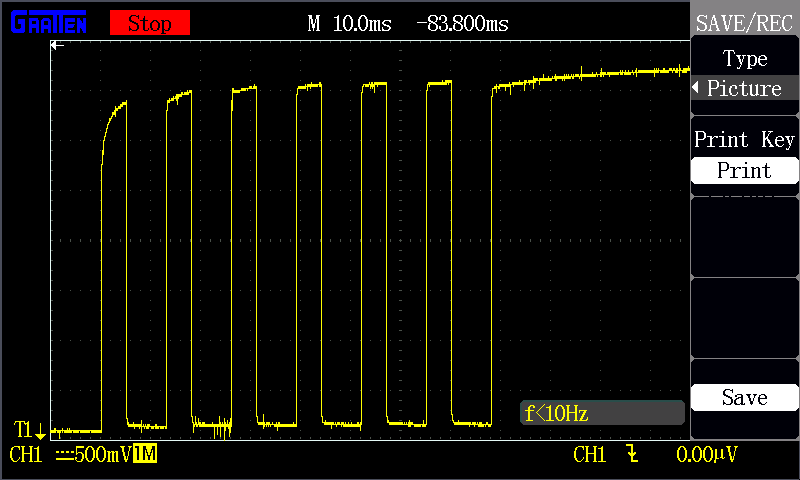

Fig. 1: TTL4 output, the rising time on the first pulse seems more obvious than the rest; the first 6 pulses also couldn't fully rise to 3.7 V like the final pulse in this period.

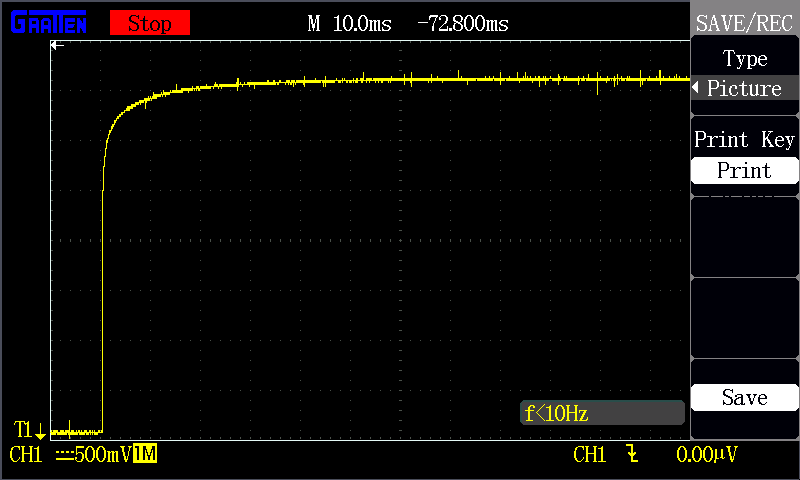

Fig. 2: TTL5 output, which is also similar to TTL7 output.

From the graph for TTL4, it takes 5 ms (the span of the first pulse) to rise to around 3.4 V. From the graph for TTL5, it also takes around 5 ms to rise to 3.4 V. The rising times for these outputs match.

However, we do not expect a DIO having this long rising time. We expect the oscilloscope to show clear and straight square-waves at this magnification level.

The conclusion is the issue comes from the SMA DIO, not your code or ARTIQ.

Edit: an issue is now open on sinara-hw's repo.