Based on the code in https://github.com/m-labs/artiq/blob/master/artiq/gateware/rtio/core.py and https://github.com/m-labs/artiq/blob/master/artiq/gateware/rtio/sed/lane_distributor.py, I would have expected the SED to switch lanes when a FIFO gets full. However, when I run the following MWE, it seems that the SED blocks when the fifo becomes full and only continues once events start to get taken out:

`

from artiq.experiment import delay_mu, EnvExperiment, kernel, ms

class RtioFifoFull(EnvExperiment):

def build(self):

self.setattr_device("core")

self.setattr_device("aux_trigger")

@kernel

def run(self):

n_pulses = 100

self.core.reset()

delay(100 * ms)

for _ in range(n_pulses):

self.aux_trigger.on()

delay_mu(40)

self.aux_trigger.off()

delay_mu(40)

`

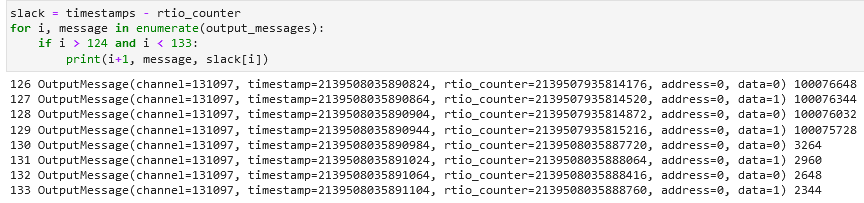

This experiment underflows. Artiq version used comes from master branch of a private repo forked from m-labs/master. As far as I can tell, there are no changes in that repo compared to m-labs/master that would cause a difference in behaviour here. Looking at core analyser, it seems that all the slack gets eaten up between events 129 and 130 (one-indexed). I am surprised that it's not between events 128 and 129 as this should be when the fifo of the first lane becomes full.

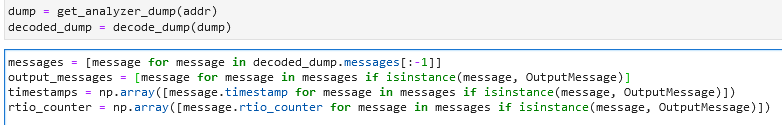

Relevant bits of code:

Is this expected behaviour or a bug?