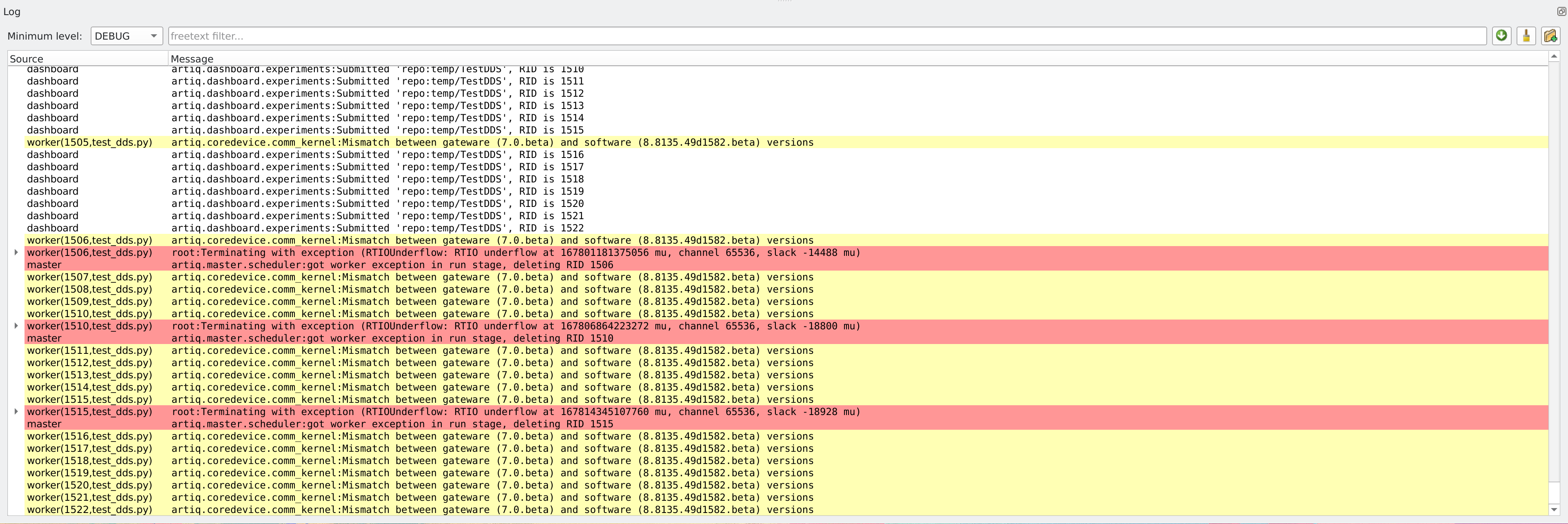

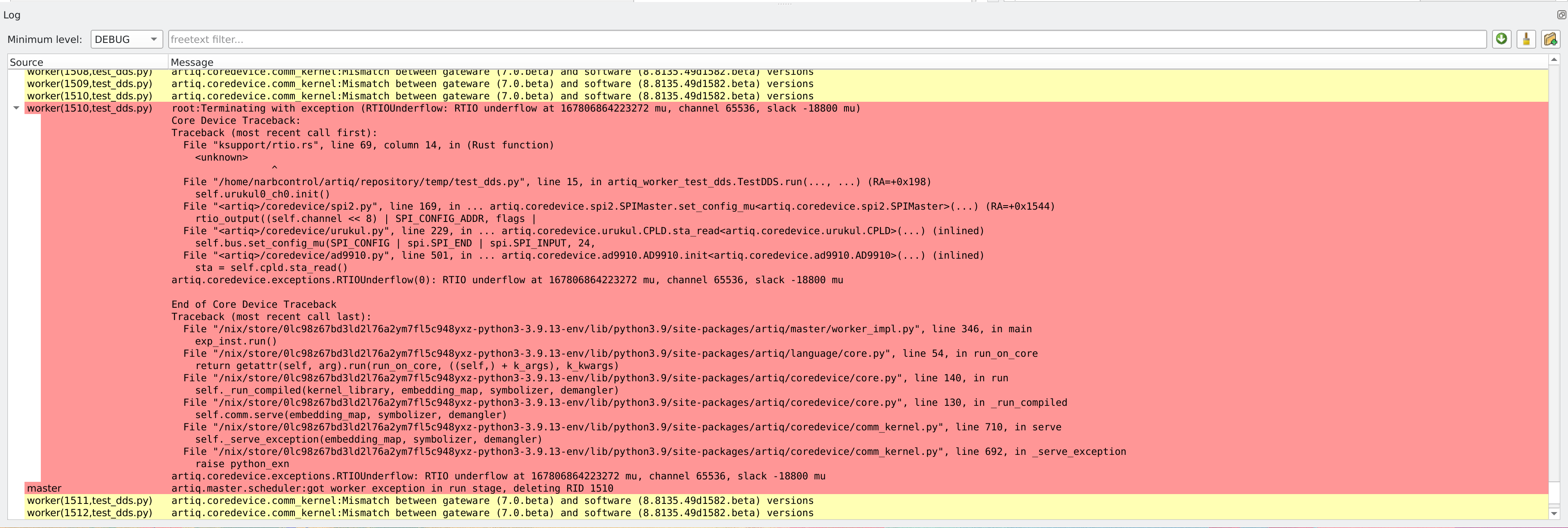

Recently I encountered a weird problem that random RTIO underflow occurs in dds.init() function. I finally figured out that it is due to the function ad9910.set(). The sample code below will sometimes cause a slack of around -18μs in dds.init() if I submit this experiment many times. And adding delay before dds.init() doesn't help. Is there any way to solve this?

from artiq.experiment import *

class TestDDS(EnvExperiment):

def build(self):

self.setattr_device("core")

self.setattr_device("urukul0_ch0")

self.setattr_device("urukul0_cpld")

@kernel

def run(self):

self.core.reset()

self.urukul0_cpld.init()

delay(10 * ms)

self.urukul0_ch0.init()

delay(10 * ms)

self.urukul0_ch0.sw.on()

delay(10 * ms)

self.urukul0_ch0.set(1 * MHz)

. This time the error log says

. This time the error log says