- Edited

I am interested in STFT pulsegen to generate consecutive pulses that has carrier phases fixed to the time zero of pulse sequences. I spent a month to see outcome of STFT example included in Phaser STFT branch.

The problem I found is that STFT functionality is not enabled in Ch1.

To ask your help and share my problem, I clarify what I have setup for this test.

I should ask for help directly to the pulsegen developer Norman Krackow. But I am not sure mine is hardware problems. So I leave here, feeling sorry if this seeking help bothers community.

Environment

- Ubuntu 22 (LTS)

Phaser firmware

- QUATIQ Phaser STFT-pulsegen branch

git clone https://github.com/quartiq/phaser.git --branch stft_pulsegen

ARTIQ

- Starting from the released ARTIQ-7, I modify files:

$(ARTIQ)/coredevice/phaser.py

$(ARTIQ)/gateware/rtio/phy/phaser.py

$(ARTIQ)/gateware/eem.py.

The modification of code-works followed to works by the developer Norman Krackow. I just copied and pasted his commits in Quartiq/Artiq branch stft_pulsegen.

Installation

- "nix develop" in the modified ARTIQ-7 main directory.

- In the same nix shell, I compiled the phaser stft-pulsegen firmware by "python phaser.py"

- I flashed using vivado and flash.tcl. (and hardware Xilinx platform cable II).

- I compiled Artiq firmware as the manual's guideline using the original json description, and flashed using "artiq_flash".

Results

- $(phaser git repository pulsegen branch)/stft_pulsegen_example/spetralspass.py example code

- $(phaser git repository pulsegen branch)/stft_pulsegen_example/timing.py example code

Problem observed

The example code "spectralspass.py" seem to emit signals Ch1 and Ch2, and "timing.py" emits to Ch1.

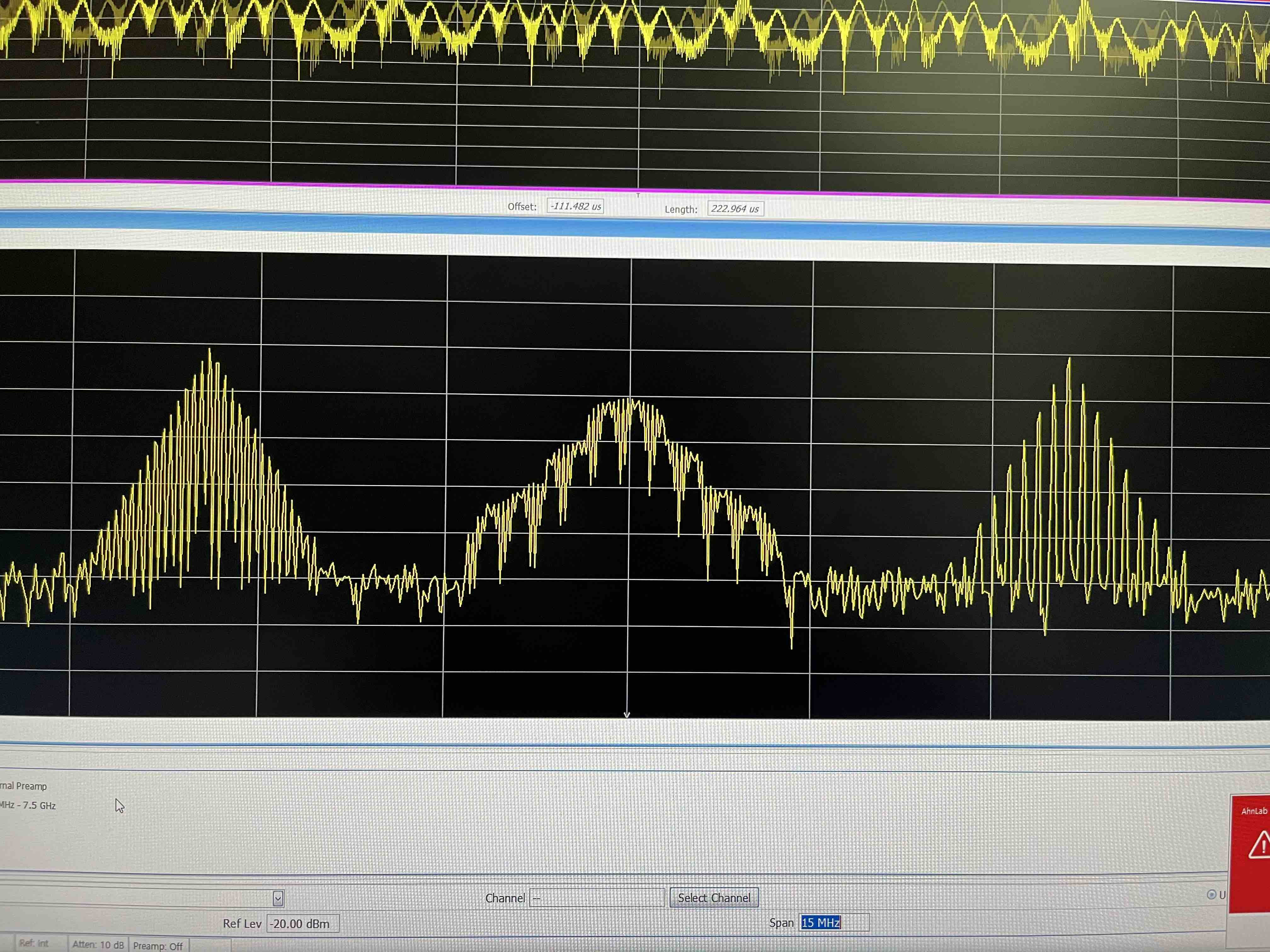

- But the signal only appears Ch2 for "specktralspass.py",

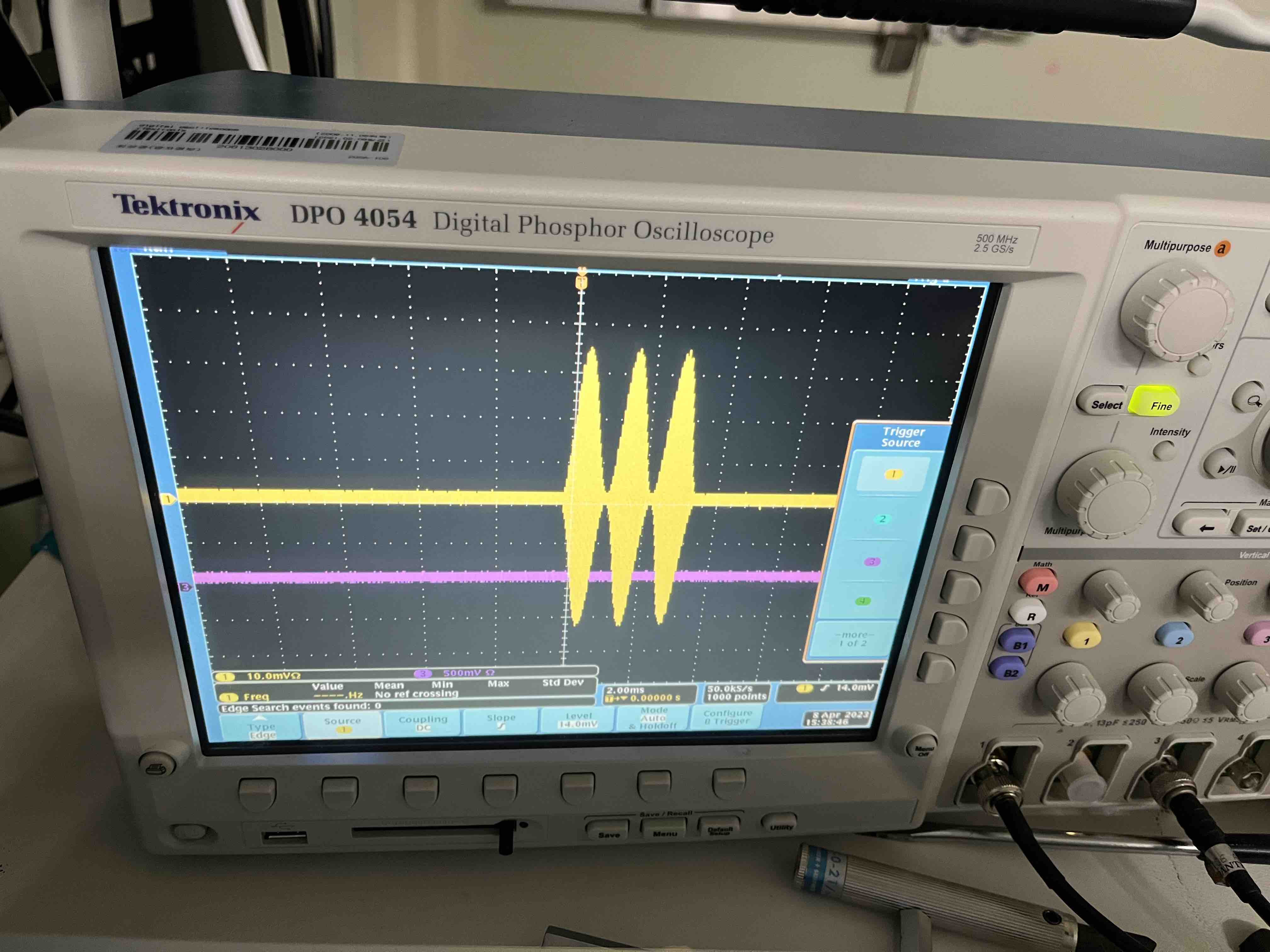

- and "timing.py"' shows only channel DUC (not showing pulse envelope, but DUC oscillator carriers):

For "timing.py" case, results in Ch1 are exactly the one attained after I disabled (flag, or removed lines of STFT setting) STFT. - The desired 3-pulse figure was achieved in Ch2, which I enabled by modification:

for ch in range(2):.

I hope this problem to remain software areas. I am afraid whether ch1 circuits is broken due to user mishandling.

Thank you very much.