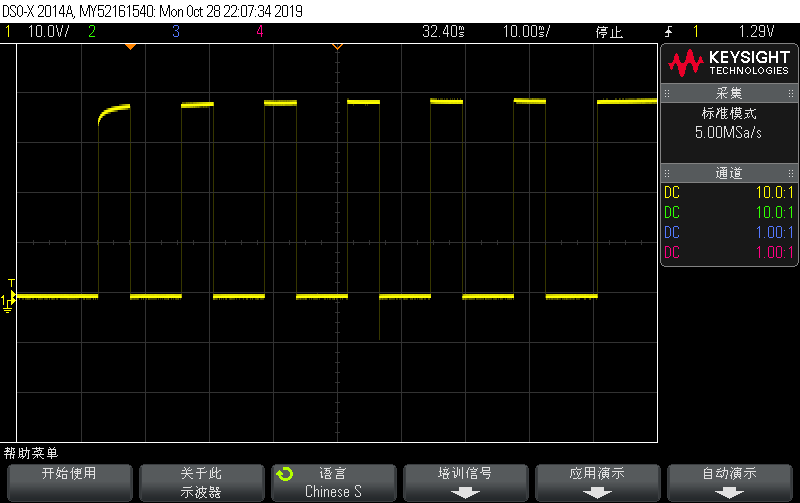

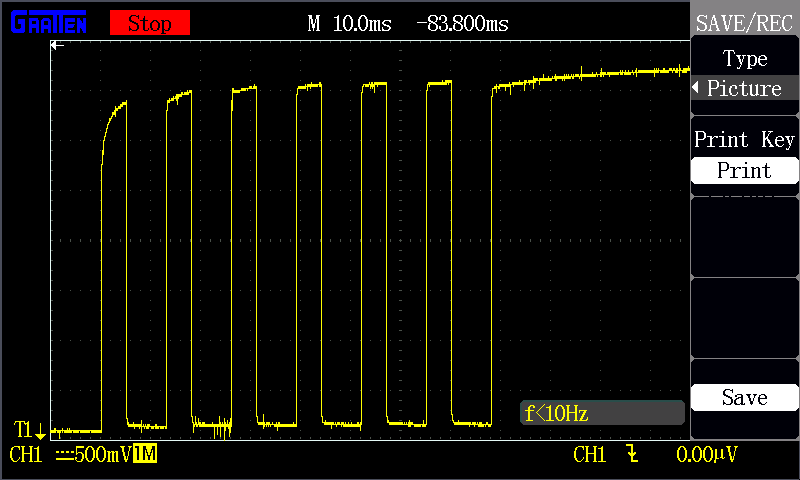

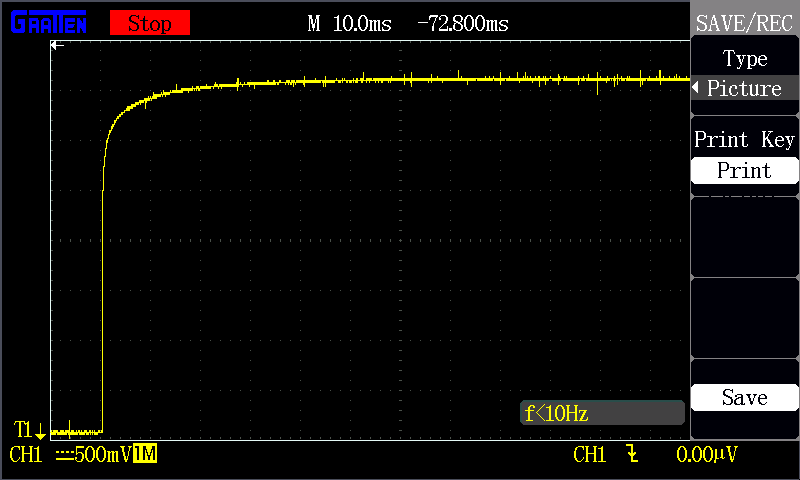

the first wave of the output of the TTL has an obvious rising edge ,but the second or the third wave has not the situation,

the following are the codes and the picture is output of the ttl4

from artiq.experiment import *

def print_underflow():

print("RTIO underflow occured")

class Tutorial(EnvExperiment):

"""101-两路TTL时序测试V3

"""

def build(self):

self.setattr_device("core")

self.setattr_device("ttl4")

self.setattr_device("ttl5")

self.setattr_device("ttl6")

self.setattr_device("ttl7")

@kernel

def t4(self):

delay(77*ms)

self.ttl4.pulse(5*ms)

delay(8*ms)

self.ttl4.pulse(5*ms)

delay(8*ms)

self.ttl4.pulse(5*ms)

delay(8*ms)

self.ttl4.pulse(5*ms)

delay(8*ms)

self.ttl4.pulse(5*ms)

delay(8*ms)

self.ttl4.pulse(5*ms)

delay(8*ms)

@kernel

def run(self):

self.core.reset()

delay(20*ms)

try:

for i in range(10000000):

with parallel:

self.ttl4.pulse(400*ms)

self.ttl5.pulse(400*ms)

self.ttl6.pulse(400*ms)

self.ttl7.pulse(400*ms)

with parallel:

self.ttl5.pulse(130*ms)

self.ttl6.pulse(130*ms)

self.ttl7.pulse(130*ms)

with parallel:

self.ttl6.pulse(400*ms)

with parallel:

self.t4()

self.ttl6.pulse(155*ms)

except RTIOUnderflow:

print_underflow()