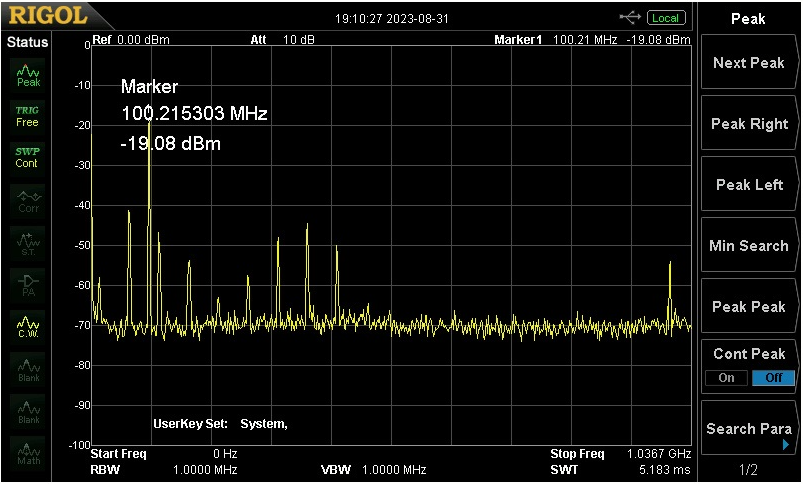

I am trying to set up the Urukul with an external low noise 1 GHz clock. The output frequency is correct, but there are other frequencies jumping around. I can see the 1 GHz leaking, the expected 100 MHz output, but also other frequencies, which are changing quicker than the refresh rate of the spectrum analyzer. I tried -5 dBm and 5 dBm for the clock.

I'm not sure if I configured everything correctly:

The flash configuration is set to:

{

"type": "urukul",

"hw_rev": "v1.5.2",

"ports": [

5,

6

],

"synchronization": true,

"clk_sel": 1,

"pll_en": 0,

"refclk": 1e9,

"clk_div": 1

}

In the (generated) device_db I added/changed:

device_db["urukul0_cpld"] = {

"type": "local",

"module": "artiq.coredevice.urukul",

"class": "CPLD",

"arguments": {

"spi_device": "spi_urukul0",

"sync_device": "ttl_urukul0_sync",

"io_update_device": "ttl_urukul0_io_update",

"refclk": 1e9,

"clk_sel": 1,

"clk_div": 1

}

}

And for all DDS channels on that Urukul:

device_db["urukul0_ch0"] = {

"type": "local",

"module": "artiq.coredevice.ad9910",

"class": "AD9910",

"arguments": {

"pll_en": 0,

"chip_select": 4,

"cpld_device": "urukul0_cpld",

"sw_device": "ttl_urukul0_sw0",

"sync_delay_seed": "eeprom_urukul0:64",

"io_update_delay": "eeprom_urukul0:64"

}

}

The script used:

from artiq.experiment import *

import numpy as np

from artiq.coredevice.ad9910 import _AD9910_REG_FTW

class DDSTest(EnvExperiment):

def build(self):

self.setattr_device("core")

self.setattr_device("urukul0_cpld")

self.setattr_device("urukul0_ch0")

def run(self):

self.initialize()

self.set_values()

@kernel

def initialize(self):

self.core.break_realtime()

self.urukul0_cpld.init()

self.urukul0_ch0.init()

@kernel

def set_values(self):

self.core.break_realtime()

delay(100*us)

self.urukul0_ch0.set(100e6)

self.urukul0_ch0.sw.on()